文章编号:1673-0062(2013)01-0031-06

# 一种 μ 子成像触发逻辑电路的设计

袁 勇1,2,王红艳2,龚学余1\*,刘志英2

(1. 南华大学 核科学技术学院,湖南 衡阳 421001; 2. 中国原子能科学研究院,北京 102413)

摘 要:在宇宙射线 μ 子成像系统中,触发逻辑电路是触发判选系统的重要组成部分,其作用是快速实时的对有效 μ 子事例进行选择,并产生触发信号. 本文主要介绍了宇宙射线 μ 子成像系统触发信号的实现原理以及用 Verilog HDL 设计实现触发逻辑电路.

关键词:μ 子成像;触发逻辑电路;触发信号;Verilog HDL

中图分类号:TL822 文献标志码:B

### The Design of Trigger Logic Circuitry in Muon Radiography

YUAN Yong<sup>1,2</sup>, WANG Hong-yan<sup>2</sup>, GONG Xue-yu<sup>1\*</sup>, LIU Zhi-ying<sup>2</sup>

(1. School of Nuclear Science and Technology, University of South China, Hengyang, Hunan 421001, China;2. China Institute of Autornic Energy, Beijing 102413, China)

**Abstract:** In the Cosmic Ray Muon Radiography, the trigger logic circuitry is the key part of the trigger system, and its role is to quickly select valid muon in real-time and generate the primal trigger signal. This paper presents the implement principle of trigger signals of Cosmic Ray Muon Radiography system. Verilog HDL is used to design the trigger logic circuitry.

key words: Muon Radiography; the trigger logic circuitry; the trigger signal; Verilog HDL

近些年来,核材料和放射源失窃、走私等现象时有发生,反核与辐射恐怖越来越引起国际社会的关注,防止核材料走私已成为反恐斗争中一项重要的任务.

宇宙射线 μ 子探测裂变核材料技术<sup>[1]</sup>解决 了防护层屏蔽、辐射源健康危害、无法真正识别裂 变核材料等问题,和传统的 γ 射线和中子等探测 技术相比,能穿透 2 m 厚的铅屏蔽层,辐射源天然存在,能识别重核材料等优点,将成为未来海关、车站及机场重核材料走私或非法运输的检测手段之一.

目前宇宙射线 µ 子成像装置正处于预研制和方案设计阶段,触发逻辑电路是该技术触发判选系统的重要组成部分,其作用是通过逻辑符合

快速实时地选出有效的 μ 子事例,排除无效事例 并为系统提供触发信号,使得在线读出系统只记录好事例数据以便数据判选系统进一步对数据进行软件筛选. 国内外主要有北京谱仪<sup>[2]</sup>、ATLAS MDT<sup>[3]</sup>等大型实验对触发判选系统的研究比较多,但对其中触发信号的实现电路没有详细的介绍,本文通过 Verilog HDL 设计实现了一种简单实用的触发逻辑电路.

### 1 用于μ子成像的位置灵敏探测器

一般来讲,适应于探测带电粒子的探测方法和探测器都适用于  $\mu$  子, $\mu$  子成像装置探测器的选择需要对性能要求、类型结构和技术条件等进行综合考虑<sup>[4]</sup>.

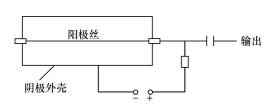

漂移管:漂移管是一种性能优越的同轴圆柱小漂移室,在粒子探测器发展的早期就已经发展起来并得到不断的改进<sup>[3]</sup>.通过外接电路可以测量其漂移时间,漂移管的空间分辨能力很高.装置采用直径 30 mm,管壁为铝金属材料的漂移管,管内充满氩和二氧化碳等气体,其中管壁作为阴极,在管的轴线上拉有直径约 50 μm 的镀金钨丝作为阳极灵敏丝,阳极丝通过绝缘材料与阴极外壳绝缘开,工作时在漂移管阴极和阳极之间加上千伏的高压,入射粒子与管内气体作用产生的离子对在电场的作用下分别向阴极、阳极漂移.漂移管探测器如图 1.

图1 漂移管探测器示意图

Fig. 1 Schematic of drift tube

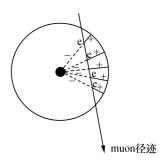

根据漂移管的设计参数,电离电子在气体中的平均漂移速度约为3.0 cm/μs. 漂移距离是一个随机量,取决于 μ子的入射位置. 显然,最大漂移距离为管子半径长度,在不考虑扩散和电场不均匀性的影响下,可求得电子在飘移管中最大漂移时间<sup>[5]</sup>. 如图 2 所示为 μ 子穿过漂移管的示意图.

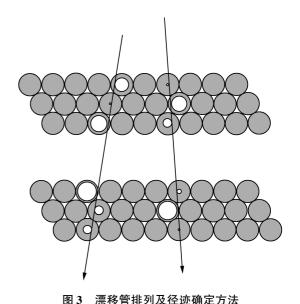

每组位置灵敏探测器由六层漂移管组成,上 三层沿横方向交错排列,下三层沿纵方向交错排 列,从 r-Φ 平面看相邻的两层漂移管的排列互相 错位,如第2层的漂移管丝的位置正好在第1层两根漂移管之间,第3层的排列同第1层,没有探测死区.如图3所示为两组探测器X方向的漂移管排列及径迹确定方法<sup>[67]</sup>.

图 2 μ子穿过漂移管的示意图 Fig. 2 Ionization of the gas along a muon track crossing a drift tube.

Fig. 3 The drift tube arrangement and the track determining Methods

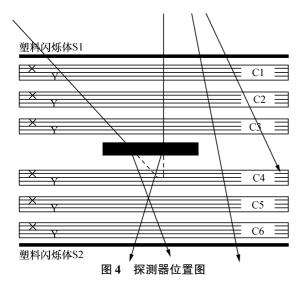

六组位置灵敏探测器如下图 4 所示叠放,分别为 C1、C2、C3、C4、C5 和 C6,每组探测器沿垂直方向间隔一定距离,最上层灵敏探测器 C1 上面和最下层灵敏探测器 C6 下面各放置一个塑料闪烁体探测器(S1、S2),目的是为系统提供触发信号,中间为被探测对象.每组灵敏探测器上三层漂移管与下三层漂移管的丝方向互相垂直,这样每组探测器就可以确定一个轨迹点.被探测物体上面的三组探测器可以确定三个轨迹点,根据这三个轨迹点即可确定 μ子入射的轨迹.同理被测物体下面的三组探测器可以确定 μ子出射的轨迹.根据入射和出射轨迹可

以得到  $\mu$  子经过物体的散射角,统计散射角分布就可以通过成像算法进行图像重建<sup>[8]</sup>.  $\mu$  子平均寿命约为 2. 2  $\mu$ s,在海平面的注量率约为 10 000 /  $(m^2 \cdot min)$ ,穿过整个成像装置的时间约 10 ns,其寿命对测量的影响可以忽略.

Fig. 4 Schematic representation of detector positions and object area

# 2 触发逻辑电路

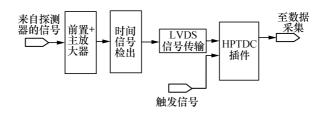

从漂移管阳极丝输出的信号经耦合电容、放大电路、甄别器剔除幅度较小的噪声信号后,一路送入时数转换器完成时间数字转换;另一路送入触发逻辑插件,经逻辑符合筛选出有效的 μ 子事例并为时间数字转换器提供触发信号.

### 2.1 漂移管信号的处理

信号从漂移管阳极丝输出后进入前置放大和主放大器,随后送入定时电路,经定时甄别电路定时以及剔除幅度较小的噪声信号,转换成 LVDS 差分信号,LVDS 信号经长距离传输最终送入高性能时间数字转换器(HPTDC),只有当触发端口的触发逻辑信号对 HPTDC 进行触发时,HPTDC 才开始对从漂移管探测器过来的各路信号进行读取和存储,存储模块的信息将送入计算机数据采集系统进行进一步的数据判选,漂移管信号的处理流程如图 5.

图 5 μ子探测器信号处理流程

Fig. 5 Signal flow diagram for muon detector signal processing

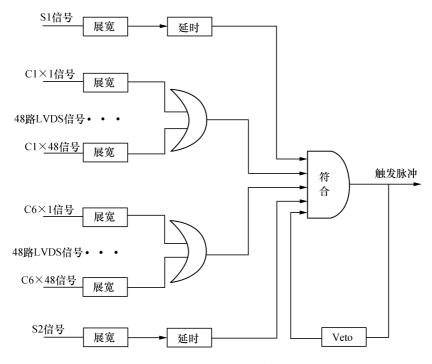

### 2.2 触发逻辑信号的实现原理

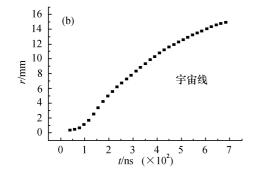

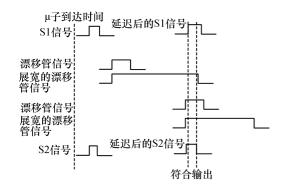

同一个 μ 子穿过六组灵敏探测器和上下闪烁体探测器时,会在漂移管及闪烁体探测器上产生脉冲信号,这种 μ 子事例称之为一个可用的好事例,当一个好事例出现时,触发逻辑电路需要为时间数字转换器提供一个触发逻辑信号. 触发逻辑电路设计的原理:将来自 C1 和 C6 漂移管探测器的 96 路信号分别进行展宽,与经过展宽及延时后的 S1、S2 信号一起送入符合模块,四路信号经符合输出触发逻辑信号,触发逻辑电路框图如图 6 所示. 闪烁体探测器输出的信号往往存在很多噪声,用两个闪烁体探测器输出的信号往往存在很多噪声,用两个闪烁体探测器输出的信号往往存在很多噪声,用两个闪烁体探测器的目的是减少误触发. 由于 μ 子在穿过漂移管时,漂移时间的大小由 μ 子穿过漂移管的位置决定,漂移距离和漂移时间 (r-t)的关系如图 7<sup>[9]</sup>,这样就使得同一 μ 子穿

过漂移管时从阳极丝输出的信号不同步,在输入符合模块时与 S1、S2 信号不一定有符合输出,我们对信号做如下的两步处理:

- 1. 对 S1、S2 信号进行一定的延时;

- 2. 将漂移管输出的信号展宽到 1 000 ns.

那么不管这个 µ 子是从漂移管的哪个位置 穿过都能产生符合输出,信号时序如图 8 所示. 由 此可知,只有相应满足时序要求的 µ 子好事例才 能符合输出触发逻辑信号,从而排除了大量的不 满足要求的 µ 子事例.

由于时间数字转换器(TDC)需要一定的时间 读取和存储来自漂移管探测器的信号,所以在一个 触发信号发出 1 μs 后才允许随后的触发逻辑信号 产生,以保证 TDC 被触发后有足够的时间来处理 阵列信号,电路加入了一路 Veto 反符合输出.

图 6 触发逻辑电路框图

Fig. 6 Schematic of trigger logic

图 7 漂移距离与漂移时间(r-t)关系

Fig. 7 The so-called rt-relation correlates the drift time with the drift radius R in respect to the anode

图 8 信号时序图

Fig. 8 The timing diagram of signal

# B 用 Verilog HDL 对电路的设计描述

Verilog HDL是一种硬件描述语言,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模过程,广泛应用于数字电路系统设计,Verilog HDL语言允许设计者进行各种级别的逻辑设计,以及数字逻辑系统的仿真验证、时序分析、逻辑综合[10].

#### 3.1 Verilog HDL 描述的总体结构

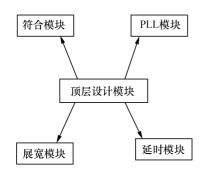

要用 Verilog HDL 对逻辑电路进行描述,首先应根据设计需求进行电路设计.这里采用自上而下的设计方法.按照上述电路的设计要求及实现的需要用 Verilog HDL 进行描述,整个电路描述由5个 Verilog HDL 文件组成,设计中采用 Verilog HDL 的分层次的结构进行描述,一方面使整个设计的结构层次分明,另一方面使每部分的设计变得相对简单,可以对各个部分进行单独的设计和模拟,如图 9 为主要的设计实体及它们之间的联系.

#### 3.2 部分电路的设计说明

触发逻辑电路各个功能模块电路的设计都是在充分考虑 FPGA 的资源和结构特点利用 Verilog HDL 描述而实现的,这里仅对其中部分电路模块作简单的说明.

图 9 Verilog HDL 描述的总体结构 Fig. 9 The overall structure of Verilog HDL

#### 3.2.1 延时及展宽模块的电路设计

在电路设计中需要对 S1、S2 信号进行延时以及对所有输入信号进行展宽,这样就需要设计延时器及展宽电路,实现延时和展宽电路有两种可能的方法,一种是在 FPGA 芯片外使用延时芯片和单稳态电路实现,另一种是在 FPGA 芯片内设计延时模块和展宽模块.使用外部延时芯片和单稳态电路的设计方法虽然可以减少 FPGA 内的设计,但这将使 FPGA 外部电路变得相当复杂,并且增加了电路设计的难度和工作量,因为这样还必需在 FPGA 芯片外设计完整的读写系统,信号也必然会反复地从 FPGA 芯片内引入引出.所以,这里采用了第二种方法.

在 FPGA 内有丰富的触发器资源,以及可以利用触发器组成计数器,通过触发器以及触发器组成的计数器实现延时和信号展宽功能,这就是设计的基本思路. 这样的设计方法需要一个计数的时钟,利用晶振的 50 MHz 时钟经 PLL 倍频到100 MHz.

延时模块的设计是首先通过移位寄存器实现一固定的延迟时间,然后根据需要在固定延迟时间后实现以1个时针周期为步长的微调;展宽模块的设计思路是当 C1、C6 端口有信号输入时,对输入的信号进行展宽,展宽时间为1000 ns,当前一个脉冲展宽还未完成而后续仍有脉冲信号输入时,就在前一个脉冲展宽的基础上,以后续脉冲上升沿为起始点,继续展宽1000 ns,依此类推.

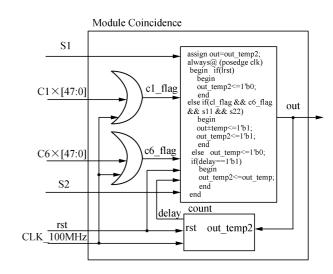

#### 3.2.2 符合模块的设计

符合模块的实现是先将每组 48 路的漂移管信号分别相或,然后再与经过延时的 S1、S2 信号相符合输出,每产生一个触发信号后 1 000 ns 内将拒绝新的触发信号产生. 图 10 给出了利用以上思路设计的符合模块框图. 其中 C1、C6、S1、S2 为符合输入信号,

Fig. 10 The block diagram of coincidence modules

符合模块框图

图 10

out 为输出信号,48 路 C1 信号以及 48 路 C6 信号先分别相或,CLK\_100MHz 为 100 MHz 输入计数脉冲,可用 50 MHz 的晶振通过倍频得到,rst 端连接到系统的 reset 上,系统复位后,当 S1、S2、c1\_flag、c6\_flag 信号不全为 1 时,输出计数器置"0",输出端 out 为低电平,只有当 S1、S2、c1\_flag、c6\_flag 信号全为 1 时,输出端 out 才为 1,此时,计数器开始计数,当计数器计到 1 μs 时,输出 out 变为低电平,计数器停止工作,符合模块对输入的数据重新进行符合.

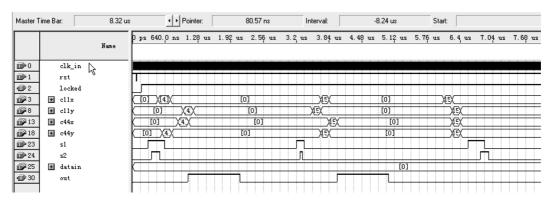

### 4 FPGA 对触发逻辑信号的实现

通过模拟一个好事例穿过成像装置时的情况对设计电路进行时序仿真,从时序仿真的结果可以看出,当输入信号满足要求时,相应的会输出一个触发信号,如图 11. 触发逻辑由一片 Altera 公司的 EP2C35F484C8N FPGA 芯片实现,该芯片最大逻辑单元数为 33216,一共有 484 个引脚,其中可用 L/O 引脚 322 个,在本设计中 FPGA 接收的所有输入信号都为高速 LVDS 信号,所以需要 98 对 LVDS 接收引脚,一共使用了 235 个 L/O 引脚,使用率约为 73%. 为了绘制印制电路板的需要,每个输入输出端口都被固定在确定的引脚上,引脚的固定将对 FPGA 内的布线产生一定的限制.

# 5 结 论

这种基于 FPGA 的触发逻辑电路能实时而有 效地进行有效 μ 子事例的选择,用 Verilog HDL 硬件描述语言来设计实现该电路,通过对电路进 行模块化设计的方式,对于今后该电路功能和模 块的扩展以及修改都提供了极大的便利,在宇宙 射线 μ 子成像装置上的应用是完全可行的.

图 11 触发逻辑信号时序仿真图

Fig. 11 The timing simulation diagram of the trigger logic signal

#### 参考文献:

- [1] Schtltz L J. Cosmic ray muon radiography [D]. Portland: Portland State University, 2003.

- [2] 王贻芳. 北京谱仪的设计与研制[M]. 上海: 上海科学技术出版社, 2011.

- [3] Arai Y, Ball B, Beretta M, et al. ATLAS muon drift tube electronics [J]. J/NST 3,2008,3(9): P09001.

- [4] 罗炜,王红艳,陈凌,等.用于核材料检测的两种宇宙射线  $\mu$ 子位置灵敏探测器[J].核电子学与探测技术,2009,29(2):353-355.

- [5] 庞洪超. 宇宙射线 μ 子探测高原子序数材料的成像 研究[D]. 北京:中国原子能研究院,2010.

- [6] Green J A, Alexander C, Asaki T, et al. Optimizing the

- tracking efficiency for cosmic ray muon Tomography [C]//IEEE Nuclear Science Symposium Conference Record, SanDiego, CA; 2006, 11, 285-288.

- [7] Engl A, Hertenberger R, Biebel O, et al. Temperature studies for ATLAS MDT BOS chamber. IEEE Nuclear Science Symposium Conference Record. 2008, N30-198

- [8] 窦飞. 高 Z 物质宇宙线成像系统读出电子学方法研究[D]. 合肥:中国科学技术大学,2012.

- [9] 欧阳群,庄胥爱,谢一冈,等. 高气压精密漂移管的时间性能研究[J]. 高能物理与核物理,2005,29 (4);397.

- [10] 夏宇闻. Verilog 数字系统设计教程[M]. 北京:北京 航空航天大学出版社,2008.