文章编号:1673-0062(2009)01-0056-05

# 基于 FPGA 的全数字化移相 PWM 控制器设计

陈文光1,饶益花2,韦瑞锦1,单长虹1

(1. 南华大学 电气工程学院,湖南 衡阳 421001; 2. 南华大学 数理学院,湖南 衡阳 421001)

要:移相脉宽调制在大功率开关电源控制中有着广泛的应用.本文介绍了一种新 型的基于 FPGA 的全数字化移相脉宽调制控制器,并使用 VHDL 语言和有限状态机 法设计了控制器中 DPWM、ADC 等多个模块. 最后通过一台 500W/48V 样机对设计 的控制器进行可行性实验验证,结果表明该数字控制器能实现预订的功能以及零电 压软开关,效率达到91%,此方法设计的移相脉宽调制器的特点是能实现开关电源 控制的全数字化.

关键词:可编程逻辑器件;移相脉宽调制;全数字化 PWM;开关电源

中图分类号:TN4

文献标识码:A

## Design of All Digital Phase - Shift PWM Controller based on FPGA

# CHEN Wen-guang<sup>1</sup>, RAO Yi-hua<sup>2</sup>, WEI Rui-jin<sup>1</sup>, SHAN Chang-hong<sup>1</sup>

- (1. School of Electrical Engineering, University of South China, Hengyang, Hunan 421001, China;

- 2. School of Mathematics and Physics Science, University of South China, Hengyang, Hunan 421001, China)

Abstract: Phase - shift pulse width modulation (PWM) has a wide application in the control field of high power switching mode power supply (SMPS). A novel all digital phase - shift PWM controller based on FPGA was proposed in the paper. Simultaneity, some modules of controller including DPWM and ADC were realized using VHDL and the method of the finite state machine. To demonstrate the feasibility of this controller, a 500W/48V power supply prototype has been assembled and tested. Experimental results are shown the digital controller can achieve the predicted function, zero - voltage soft switching and efficiency is 91%. Characteristics of this method are able to achieve switching power supply controlled by all digital.

Key words: FPGA; Phase - Shift PWM; all digital PWM; switching mode power supply

移相脉宽调制(PS - PWM)技术因其能实现 软开关技术,具有较高的转换效率,故近年来被研 究人员广泛应用于大功率电源控制中,其控制是 使用类似于 UC3875 等模拟芯片. 但设计实验时 还需要使用外部电阻、电容来确定开关频率、输出 信号之间的时序关系等,同时由于制造高频变压

收稿日期:2008-11-12

基金项目:湖南教育厅科研基金资助项目(06C716).

作者简介:陈文光(1968-),男,湖南茶陵人,南华大学电气工程学院副教授,硕士.主要研究方向:电力电子技术 与系统.

器等感性器件存在较大离散性,使得调试时繁琐.

很多学者不断尝试使用数字控制技术来设计电力电子控制器<sup>[1-3]</sup>,使得开关电源的自我诊断、自适应调节、调试和维护方便. 现场可编程逻辑器件(FPGA)是目前数字系统设计的主要硬件基础,集成度很高,其功能由逻辑结构的配置数据决定,这些配置数据可以存放在片外的 EPROM 或其他存储体上,人们可以控制加载过程,在现场修改器件的逻辑功能. 大规模可编程逻辑器件的发展给传统的电力电子控制系统设计方法带来了革命性的变化. 基于此,本文使用 FPGA 技术来设计移相脉宽调制控制器,实现了全数字化脉宽调制

技术(DPWM).

### 1 移相全桥零电压 DC - DC 开关电源

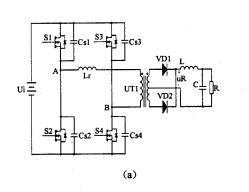

桥式逆变主电路如图 1(a) 所示.  $L_r$  为谐振电感, $C_{s1}$  ~ C s4为 MOS 管的输出电容和外加谐振电容之和.  $S_1$  、 $S_2$  为超前桥臂, $S_3$  、 $S_4$  为滞后桥臂,分析时假设图中各元件都处于理想器件,则得到图 1(b) 所示的门极驱动信号和主电路工作波形. 详细分析见文献[4]. 其设计难点是实现软开关,各驱动信号之间的时序关系与变压器、MOS 管的输出电容等参数有关.

图 1 移相全桥零电压 DC - DC 开关电源及工作波形

Fig. 1 Phase - shift ZVS full - bridge DC - DC converter and waveform

# 2 数字化移相 PWM 控制器的实现

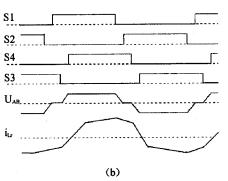

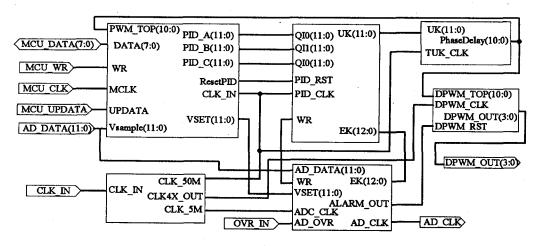

本设计采用 FPGA 实现移相全桥零电压直流 开关电源的控制,其主要由时钟控制、PID、DP- WM、ADC 采样控制等四个主要模块组成. 此外还有单片机通讯的接口模块等辅助模块,共同组成一个完整的数字化开关电源控制器. 其结构框图如图 2 所示.

图 2 FPGA 实现的数字控制器原理

Fig. 2 The principle of digital controller based on FPGA

系统在时钟模块的驱动下,通过 ADC 采样控制模块读取输出的电压值,与设定的输出值进行比较,将误差送人数字 PID 模块进行运算,得到相

应的控制量,将控制量送入 DPWM 模块,输出开 关控制信号给驱动电路,调整输出值,直到输出电 压达到系统设定值并趋于稳定.在系统工作时可 通过 MCU 接口模块与外部的处理器通讯,反馈系统工作状态,并接受新的控制参数. 设计基于 Xilinx 公司 Spartan – IIE 系列的 FPGA 芯片 XC2S100E 进行开发. 下面将对各部分进行说明.

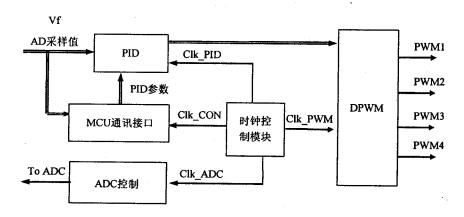

#### 2.1 DPWM 模块

实现 DPWM 的方法很多<sup>[5]</sup>,但 PS - PWM 控制比 PWM 控制要复杂,四路驱动信号的时序有严格要求,不能像一般 PWM 控制器那样用简单计数器与比较器来实现. 因此决定使用状态机来完成设计. 根据图 1(b)的控制波形,将一个周期控制过程细分为 16 个状态,不断循环来实现. 如图 3 所示,分别为:关闭 S2(s2\_off)、超前桥臂死区时间延时(st0)、打开 S1(s1\_on)、占空比延时(st1)、关闭 S3(s3\_off)、滞后桥臂死区时间延时(st2)、打开 S4(s4\_on)、半周期延时(st3)、关闭 S1(s1\_off)、超前桥臂死区时间延时(st4)、打开

S2(s2\_on)、占空比延时(st5)、关闭 S4(s4\_off)、 滞后桥臂死区时间延时(st6)、打开 S3(s3\_on)、 半周期延时(st7).

DPWM 模块启动后先初始化,将 4 路输出都置为低电平,然后开始状态循环,输出移相控制波形.在 ISE9.1 中综合得到的模块如图 6 所示,DP-WM\_TOP 为占空比延时值输入端,按照上面的计算取 11 位数据宽度,在每个周期结束时被读入DPWM 控制器,实现占空比调节. DPWM\_CLK 为时钟输入端,输入时钟频率为 200MHz. DPWM\_RST 是 DPWM 模块的复位引脚,当检测到一个高电平时,执行复位动作,DPWM 模块的输出全部变为低电平,用于在检测到 DPWM 模块工作异常时进行恢复. DPWM\_OUT 为 4 路输出信号,Bit0~Bit3 分别对应开关 S<sub>1</sub>~S<sub>4</sub>.

图 3 PWM 模块状态流程图 Fig. 3 State – flows of the DPWM module

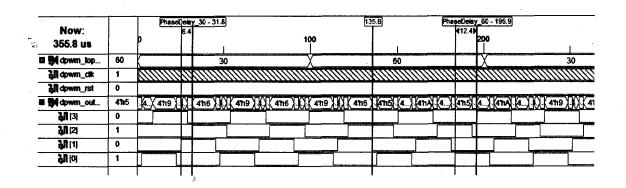

为了便于仿真测试,将模块中的 Ts 设定为 200 个时钟,死区时间设为 5 个时钟.输入测试波形相位延时时间为 30 个时钟,然后再设为 60 个时钟,观察输出的 PWM 信号是否发生了改变.仿真输出波形如图 4 所示. 从图上可知,当输入的相位延时设置由 30 变为 60 时,输出并没有马上改变,而是等到当前周期结束时,才将新的相位延时值读人控制器,在下一周期生效,这与设计的设想是一致的,在每个周期结束时才会装载新的相位设置. 当移相时间为 30 时,可以看到  $S_1$  与  $S_4$ 、 $S_2$  与  $S_3$  的相位时间间隔很短,从标注可以看到是  $6\mu s$ ,而移相时间设为 60 时的相位时间间隔是  $12\mu s$ ,正好比相位延时值为 30 时的值大了一倍. 由仿真得到的波形可以知道模块的输入输出关系与设计阶段的理论值一样,达到了设计要求.

#### 2.2 PID 控制模块

数字 PID 控制算法的实现须用数值逼近的方法. 本设计采用如下的增量式的 PID 控制算法.

$$u(k) = u(k-1) + [q_0e(k) + q_1e(k-1) + q_2e(k-2)]$$

(1)

公式(1) 中 $q_0$ 、 $q_1$ 、 $q_2$  三个参数只与 $K_p$ 、 $K_i$ 、 $K_d$  有关,只要在设定参数时计算一次即可,得到的控制增量只需要与上一次的控制量运算即为此次控制量. 据此编写 VHDL 代码,并在 ISE9.1 中综合,得到的 PID 控制器模块见图 6 所示,其中 EK 为误差输入,通过 ADC 采样比较得到,12 位数据宽度,最高位为符号位,在 WR 的上升沿时锁定并读入 PID 模块中进行运算;QIO ~ QI2 分别为 PID 运算器的三个计算参数 QO ~ Q2,11 位数据宽度,无符号位;UK 为数字控制量的绝对值输出;PID\_

CLK 为时钟输入,为运算器提供工作时钟. PID\_RST 为复位输入,高电平复位有效,此时会清除运

算器的输出,即 UK = 0;同时只有  $PID_RST = 1$  时, $QIO \sim QI2$  的值才会被读入 PID 运算器中.

图 4 DPWM 仿真波形图 Fig. 4 DPWM simulation waveforms

**G**

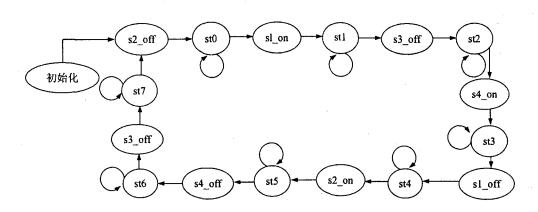

#### 2.3 ADC 控制模块

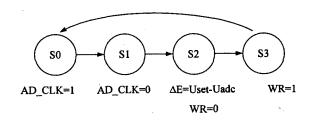

为了实现高频开关电源精确的电压调节特性,AD转换器采用闪速式(Flash)ADC,转换周期仅为一个时钟周期,因此转换速度非常快.本设计采用 ADS805,使用状态机完成 ADC 控制器的设计,状态图如图 5 所示,SO 先输出一个时钟上升信号,S1 再输出一个时钟下降信号,形成一个完整的 AD 时钟输出,S2 读取 AD 转换值,计算出误差值,并将误差值送到数据总线上,S3 给 PID 控制器发一个 WR 信号,表示新的采样误差值就绪,返回状态 SO,输出时钟上升信号.

设计得到的模块如图 6 所示. 端口 AD\_DATA 是 ADC 转换后的数据输入端口, VSET 是系统期输出望值的输入端口, ADC\_CLK 是模块的工作时钟输入, 最高为 20 MHz, AD\_CLK 是模块对 ADC输出时钟信号的端口, AD\_OVR 是溢出信号检测

口,与 ADS805 的 OVR 引脚相连, ALARM\_OUT 是异常信号输出口,当检测到异常时输出一个高电平给外部的保护电路, EK 和 WR 分别与 PID 控制器模块的 EK 和 WR 相连.

AD\_CLK = 1 AD\_CLK = 0 △E = Uset – Usdc WR = 0 WR = 1 图 5 ADC 接口状态图

Fig. 5 State - flows of ADC interface

图 6 模块连接图

Fig. 6 Modules connection graph

## 3 实验结果

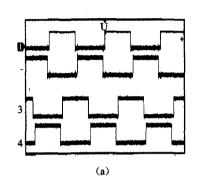

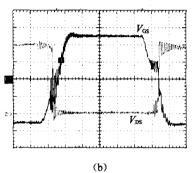

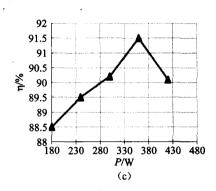

根据以上的设计思路,按照自顶向下的设计方法,在 ISE 中编写顶层文件把系统的主要功能子模块连接成一个完整的控制系统,整个系统共占用 30 个 IO 口,输出的四路信号图 7(a)所示,输出频率为 24.4 kHz. 然后将控制器应用到500 W,输出电压为 48 V 的开关电源中.在 FPGA输入时钟频率为 50 MHz 的情况下,经过四倍频

后得到 200 MHz,作为 DPWM 模块的时钟,将开关频率的宽度取 12 位,而占空比延时 t 的宽度取 11 位,此时 DPWM 输出频率为 48.8 kHz. 调试过程中,由软件合理设置上述各状态的延时,就可以方便的实现软开关. 图 7(b)为在满载的情况下,MOSFET 管电压 和栅极驱动信号 的波形,从实验波形中看出完全实现了零电压开关. 图 7(c)为实验样机在不同输出功率情况下的效率,最大效率可以达到 91.5%.

图 7 实验结果 Fig. 7 Experimental results

## 4 结束语

文中介绍了一种基于 FPGA 的全数字化移相 PWM 控制器的设计方法,对控制器的主要部分进 行了说明,并采用有限状态机法设计了 DPWM 和 ADC 控制等功能模块,并制作了一台高频开关电 源实验样机,实验结果表明该方法可行,符合设计 要求. 该方法的特点是具有在线可编程能力,简化 了设计制造流程,使调试和维护工作变得轻松. 数 字 PWM 已经表现出相当多的优点,但仍有一些 问题需要进一步研究,例如怎样提高 DPWM 的分 辨率的问题,数字化后系统动态稳定问题等.

#### 参考文献:

[1] 孟 浩, 贾 晨, 陈志良. 数字控制 PFM/PWM 混合

型 DC - DC 开关电源[J]. 微电子学与计算机,2008, 25(1):166-169.

- [2] Hwu K I, Yau Y T. FPGA Based Phase Shift ZVS Full - Bridge DC - DC Converter Using One - Comparator Counter - Based PWM Control Strategy [C]//Power Electronics and Drive Systems. PEDS07, Bangkok: IEEE. 2007:483 - 487.

- [3] Youzhu Ling, Jingmeng Liu, Bihui Luo, et al. Design of Monolithic Chip Inverter Based on FPGA[C]//Industrial Electronics and Applications, ICIEA 2007., Harbin: IEEE, 2007:2627 - 2632.

- [4] 陈 坚. 电力电子学——电力电子变换和控制技术 [M]. 北京:高等教育出版社,2002.

- [5] 张 怡,姜岩峰. 数字 PWM 技术的实现及其应用进展[J]. 半导体技术,2007,32(7):618-621.